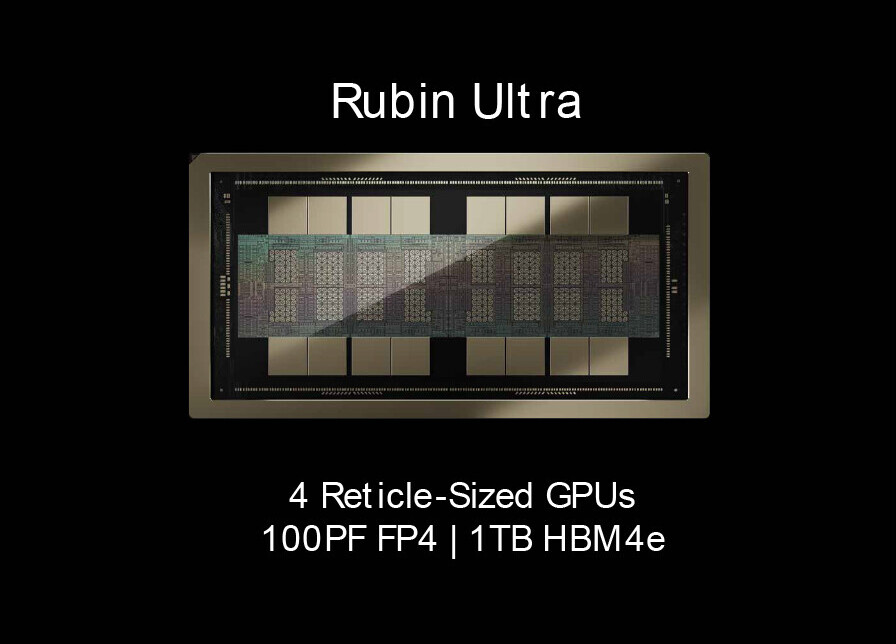

Tuesday, March 31st 2026 NVIDIA's "Rubin Ultra" Reportedly Faces Issues With CoWoS-L Packaging by AleksandarK Today, 08:50 Discuss (0 ) NVIDIA is reportedly experiencing manufacturing issues with its next-generation "Rubin Ultra" GPU design, one of the company's most ambitious chip development projects, due to the limitations of modern packaging technology. The world's largest company is already shipping customer samples of the standard "Rubin" GPUs, with mass shipments set to begin this summer. However, the current roadmap for the upgraded "Rubin Ultra" design may be encountering technological limitations, as NVIDIA's design goals are too ambitious for TSMC's packaging capabilities. Reportedly, NVIDIA plans to double the regular "Rubin" two-die package with 8 HBM4 modules into a new "Rubin Ultra" package that will include four silicon dies and 16 HBM4E modules in a single package. This configuration is scheduled for 2027, but the sheer volume of silicon may be too much for TSMC's packaging, according to Global Semi Research. In a typical CoWoS package, TSMC usually combines multiple smaller dies and multiple HBM memory modules into a unified package that supports the entire AI build-out. However, with the ambitious "Rubin Ultra" design, NVIDIA planned to use CoWoS-L, which was expected to handle the design and concept that "Rubin Ultra" was based on. It is rumored, however, that in a 2+2 die package—meaning four dies as in this architecture—TSMC is encountering warping issues. The package—which includes a substrate—is bending in multiple directions, causing the compute dies of "Rubin Ultra" to not make complete contact with the underlying substrate. This instability means that TSMC has to explore alternatives within its packaging portfolio. One of these alternatives is a panelized approach called CoPoS, which stands for Chip-on-Panel-on-Substrate. TSMC initially planned to establish CoPoS pilot lines as early as 2026, aiming for mass production between late 2028 and the first half of 2029. This change involves replacing approximately 300 mm silicon interposers with large square and rectangular panels. Early formats measure around 310 × 310 mm, with later options extending to 515 × 510 mm and even 750 × 620 mm. The larger, square format is designed to reduce wasted edge area, accommodate bigger reticles and masks for AI accelerators, and facilitate placing more dies and HBM on a single package. However, it is uncertain if CoPoS will be ready for a 2027 debut or if TSMC will need to address the CoWoS issues first. Sources: @Jukan05 on X, via HardwareLuxx Related News Tags: 2027 AI chip CoPoS CoWoS CoWoS-L development GPU HBM HBM4 HBM4E limitations memory modules Research Rubin Rubin Ultra substrate TSMC Sep 18th 2025 NVIDIA Buys $5B Worth of Intel, RTX iGPUs Coming to x86, Shares up 25% (256) Jan 16th 2026 NVIDIA Reportedly Ends GeForce RTX 5070 Ti Production, RTX 5060 Ti 16 GB Next (210) Sep 10th 2025 NVIDIA GeForce RTX 50-Series SUPER GPUs Could Arrive at CES 2026 (69) Sep 3rd 2025 NVIDIA Discrete GPU Market Share Dominance Expands to 94%, Notes Report (237) Jul 29th 2025 NVIDIA to Debut GeForce RTX 50-series SUPER GPUs by Christmas (112) Dec 31st 2025 Leaks Predict $5000 RTX 5090 GPUs in 2026 Thanks to AI Industry Demand (124) Sep 29th 2025 March-April Release of NVIDIA GeForce RTX 50-series SUPER Lineup, Possible CES Reveal (73) Feb 6th 2026 NVIDIA to Use SK hynix and Samsung HBM4 for "Vera Rubin" Without Micron (7) Mar 19th 2026 NVIDIA DLSS 5 Gets 84% Dislikes on YouTube as Backlash Grows (132) Dec 23rd 2025 NVIDIA Puts 100-Hour Monthly Limit on All GeForce NOW Subscriptions (120) Add your own on NVIDIA's "Rubin Ultra" Reportedly Faces Issues With CoWoS-L Packaging There are no yet.

31 Mar 2026, 02:42 PM

•

584 words

•

3 min

•

~3 min left

Key takeaways

- Tuesday, March 31st 2026 NVIDIA's "Rubin Ultra" Reportedly Faces Issues With CoWoS-L Packaging

Share this article