Meta has introduced a family of four Meta Training and Inference Accelerator (MTIA) chips that shift the focus from raw compute power to memory throughput and inference efficiency. Designed for real-time model serving in data centers, these accelerators promise lower latency and reduced power costs by leveraging substantial increases in HBM bandwidth and capacity.

Unlike traditional GPUs that prioritize peak arithmetic performance, Meta's MTIA series emphasizes optimized on-package bandwidth and capacity. This approach aims to cut latency while maintaining efficiency, making it particularly appealing for workloads like ranking and recommendation algorithms used in social media platforms.

The MTIA chips include hardware support for attention primitives and mixture-of-experts layers, along with low-precision formats tailored for inference. These features reduce conversion overhead and improve performance without sacrificing accuracy. Additionally, the software stack is designed to run natively on common frameworks, allowing existing production models to be deployed seamlessly on both GPUs and MTIA chips without major rewrites.

One of the most notable aspects of the MTIA series is its modularity. Multiple generations are built to share the same chassis, rack, and networking infrastructure, enabling upgrades by swapping modules rather than refitting entire data centers. This flexibility supports Meta's aggressive release cadence, which is significantly faster than industry norms, considering the scale of its data center operations spanning millions of chips.

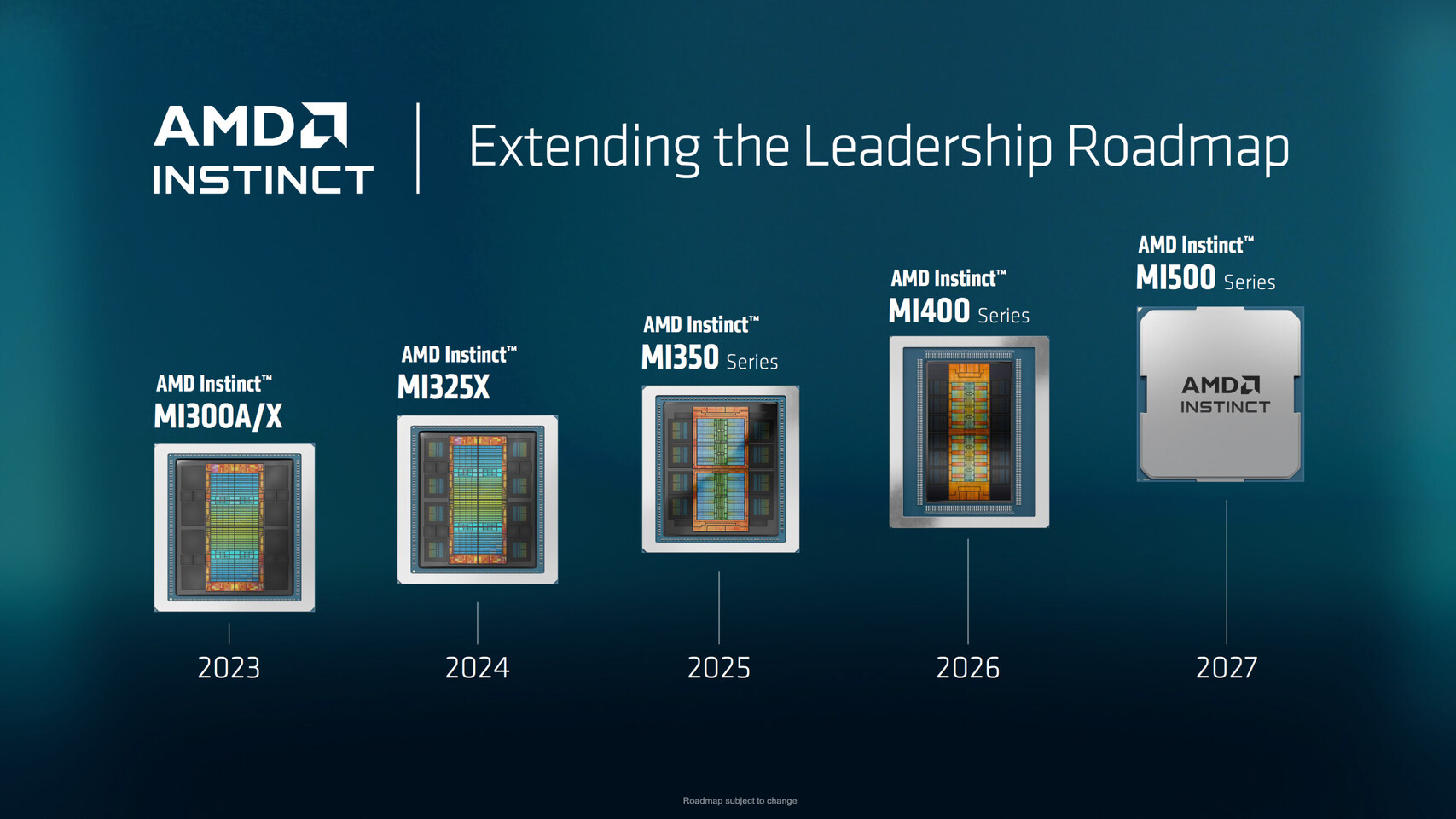

The MTIA accelerators are already operating at kilowatt power budgets and delivering PetaFLOPS levels of compute, positioning them as strong competitors to industry-leading solutions from NVIDIA, AMD, and other hyperscalers. While Meta continues to use NVIDIA and AMD GPUs for training, these new accelerators aim to balance its inference workloads, given that models are trained once but run inference continuously.

Meta's focus on in-house ASIC development is not unprecedented among hyperscalers, but it takes on added significance given the company's influence in the Open Compute Project. This initiative could see MTIA design elements integrated into broader server applications, potentially reshaping the landscape for custom silicon solutions in data centers.

The shift toward memory-centric inference accelerators marks a significant departure from traditional GPU architectures. For creators and developers working on high-performance inference tasks, these chips offer a compelling alternative to mainstream GPUs, with the potential to redefine efficiency benchmarks in data center operations.