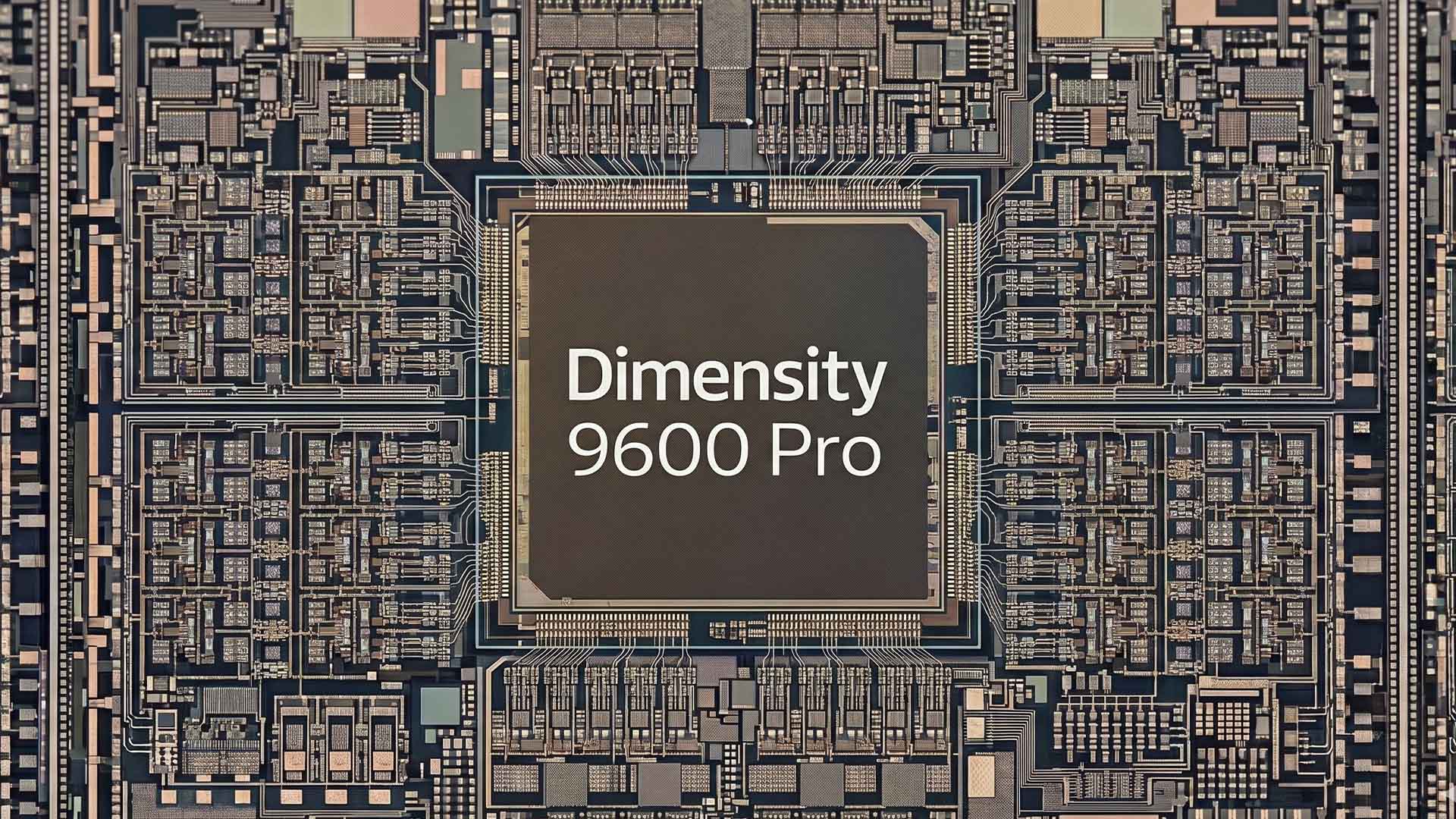

Apple Is “Materially Ramping SoIC Capacity At TSMC” As It Prepares For Its Baltra ASIC, M5 Pro/Max, M6 Pro/Max Chips, With 60K Capacity-Equivalent Wafers Reserved For 2027 Rohail Saleem • at EDT Add on Google Enter "Baltra," the internal codename given to Apple's bespoke AI server chip, which is expected to debut in 2027. Apple is beginning to lay the critical groundwork for its next-gen custom chips, including a much-anticipated server chip, dubbed Baltra, as per a new analysis from Morgan Stanley Apple is increasing its reservation slots for TSMC's SoIC packaging tech in anticipation of its next-gen custom chips, including the Baltra ASIC Morgan Stanley has noted in a fresh analysis that Apple is "ramping up" SoIC-related activity at TSMC: Related Story TSMC Has Enabled Smartphone SoCs To Approach 5GHz Frequencies Thanks To Advanced Lithography; Huawei The Biggest Loser In All Of This "Apple is materially ramping SoIC capacity at TSMC, pointing to a major push in Apple silicon for AI servers. TSMC (covered by Charlie Chan) is expanding its SoIC (System on Integrated Circuit) capacity, with Apple placing orders equivalent to 36K wafers in CY26 and 60K wafers in CY27." According to the Wall Street titan, Apple has reserved SoIC capacity that is equivalent to 36,000 wafers for the calendar year of 2026, and 60,000 silicon wafers for the calendar year 2027. For the benefit of those who might not be aware, the SoIC is a 3D packaging solution that allows for the horizontal and vertical stacking of multiple chips on to a single SoC-like chip. This new packaging also facilitates the integration of multiple individual dies - such as the CPU, GPU, and the Neural Engine - onto a single package, which provides for an unprecedented level of flexibility due to the sheer number of die configurations that then become available. For instance, if you are the artsy type, you might choose to equip the M5 Pro/M5 Max chip with a greater number of GPU cores. Of course, Apple is expected to utilize some of this oncoming capacity for the new M5 Pro and M5 Max chips, as well as the M6 Pro/Max duo that will launch next year. However, the bulk of this capacity appears destined for Apple's upcoming Baltra ASIC, which is expected to debut in 2027. As a refresher, Apple's custom AI server chip is expected to leverage TSMC's 3nm N3E process, and sport various chiplets, with each of them designed for a specific function. Apple could then combine each of these chiplets into a single unit, with Broadcom aiding in how each of these processors communicates with each other when simultaneously running in Apple Intelligence servers. This siloed approach would allow Apple to keep the overall design of the AI ASIC hidden even from its partners like Broadcom. Eventually, Apple intends to move Baltra's production in-house and remove Broadcom's role in chip designing, as evidenced by Apple's recent procurement of T-glass samples from Samsung's SEMCO. About the : Writing is my one incontrovertible passion. Over the past six years, he has authored over 2,200 distinct articles on financial and tech-related topics, spanning nearly 1 million words. And he has been a member of Wcctech mobile team since 2025. As an alumnus of the University of Toronto, Rotman Commerce Program, I bring nuance, in-depth knowledge, and a unique perspective to every topic that I cover. When I'm not writing, I'm traveling the world, exploring hidden confectionaries and restaurants as an aspiring food connoisseur. Follow on Google to get more of our news coverage in your feeds. Further Reading Apple Has Found A Clever Way To Shield Itself From The DRAM Crisis Clock Cycle: Apple’s A19 Pro Chip Beats Dimensity 9500 By 13%, Snapdragon 8 Elite Gen 5 By 10%, And Exynos 2600 By 6% Apple’s M5 Ultra Architecture Details Are Unknown, But Some Pragmatic Thinking Concludes The UltraFusion Process Will Return Samsung Will Soon Become More Profitable Than NVIDIA, And It Just Clinched An Exclusive 3-Year Display Contract From Apple Read all on Apple Is “Materially Ramping SoIC Capacity At TSMC” As It Prepares For Its Baltra ASIC, M5 Pro/Max, M6 Pro/Max Chips, With 60K Capacity-Equivalent Wafers Reserved For 2027

10 Apr 2026, 06:51 PM

•

702 words

•

4 min

•

~4 min left

Key takeaways

- Apple Is “Materially Ramping SoIC Capacity At TSMC” As It Prepares For Its Baltra ASIC, M5 Pro/Max, M6 Pro/Max Chips, Wi...

- Apple is beginning to lay the critical groundwork for its next-gen custom chips, including a much-anticipated server chi...

Share this article